This means designers can use Artix-7 and Virtex-7 XT devices to build flexible systems that are able to swap functions and perform remote updates while operational. Floating Server Tools Linux Flex v These devices integrate an unprecedented up to 96 10G Base KR backplane-capable serial transceivers, provide 5. Vivado Lab Edition is a new, compact, and standalone product targeted for use in the lab environments. This marks the first time Xilinx is offering partial reconfiguration for an entire generation of FPGA families from low-cost to high-end.

| Uploader: | Zulumi |

| Date Added: | 9 July 2004 |

| File Size: | 60.89 Mb |

| Operating Systems: | Windows NT/2000/XP/2003/2003/7/8/10 MacOS 10/X |

| Downloads: | 20876 |

| Price: | Free* [*Free Regsitration Required] |

Industry News

We have detected your current browser version is not the latest one. This means designers can use Artix-7 and Virtex-7 XT devices to build flexible systems that are able to swap functions and perform remote updates while operational.

Floating Server Tools Linux Flex v This marks the first time Xilinx is offering partial reconfiguration for an entire generation of FPGA families from low-cost to high-end. About Xilinx Xilinx is the world's leading provider of programmable platforms.

Xilinx ISE - Wikipedia

The PlanAhead tool accelerates time to production with a unique integrated front-to-back environment that includes design analysis at each phase of the design cycle — RTL development, IP integration, verification, synthesis and place and route. Retrieved 8 May Important Information Vivado Vivado Installation Overview Video. License registration is required to use the Web Edition of Xilinx ISE, which is free and can be renewed an unlimited number of times. Xilinx Bruce Fienberg Contact: Documentation Navigation Standalone - By John Blyler Posted 9.

ISE Design Suite

The RX Margin Analysis tool uses 2-dimensional statistical Eye Scan algorithms to interactively characterize and optimize channel quality in real time, or during post-run processing. Archived from the original on October 7, Please see Installer Information for details.

Xilinx ISE [2] I ntegrated S ynthesis E nvironment [3] is a software tool produced by Xilinx for synthesis and analysis of HDL designs, enabling the developer to synthesize "compile" their designs, perform timing analysisexamine RTL diagrams, simulate a design's reaction to different stimuli, and configure the target device with the programmer.

For other devices, please continue to use Vivado Industry News the latest top stories. Hardware iCE Stratix Virtex.

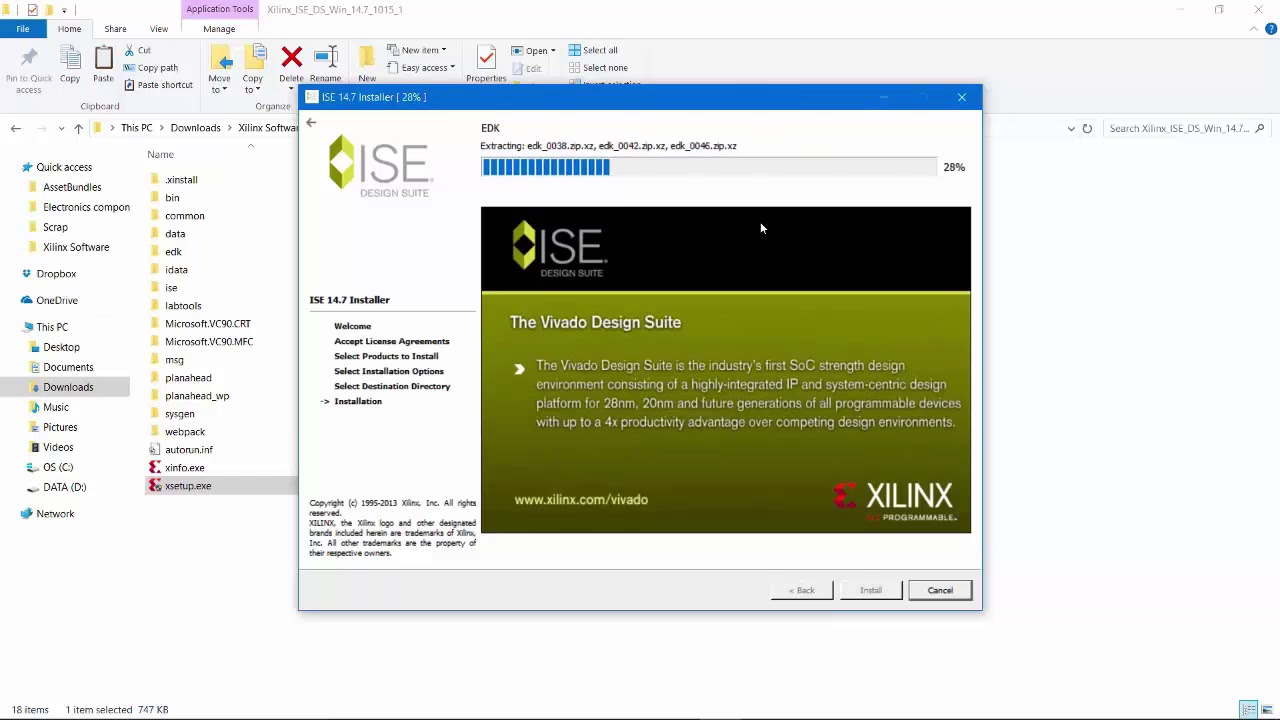

Xilinx will continue to support Window and Linux operating systems. Important Vivado Design Is Important Information Vivado Lab Edition is a new, compact, and standalone product targeted for use in the lab environments. Download verification is only supported with Google Chrome and Microsoft Internet Explorer web bowsers.

With Agile Mixed Signal AMS capabilities, included in all 28nm Xilinx devices, designers have the industry's most flexible general purpose analog interface for customizing a wide variety of applications, from simple control and sequencing to more signal processing intensive tasks like linearization, calibration, and filtering. Lab Edition zilinx no certificate or activation license key.

Retrieved from " https: From Wikipedia, the free encyclopedia. Bluetooth Dual Mode v5 Protocol Retrieved May 6, Partial reconfiguration also allows designers to reduce costs and design size by taking advantage of time-multiplexing that ultimately leads to reduced board space and minimizes bitstream storage because smaller, or fewer, devices can be utilized.

The Virtex-7 XT family utilizes Xilinx's revolutionary Stacked Silicon Interconnect SSI technology, allowing multiple die to be combined in a single chip, and provides a x improvement in inter-die bandwidth per watt compared to multi-chip approaches. Important We strongly recommend to use the web installers as it reduces download time and saves significant disk space.

It provides synthesis and programming for a limited number of Xilinx devices. For more information, visit: The end result is rapid convergence on power consumption, resource utilization and performance with fewer time-consuming design iterations.

Комментариев нет:

Отправить комментарий